## SHENZHEN LONG JING MICRO-ELECTRONICS CO., LTD.

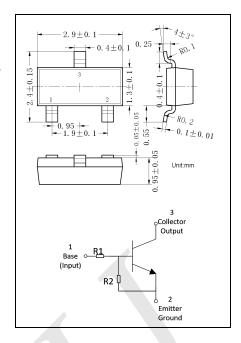

# **SOT-23 Plastic-Encapsulate Bias Resistor Transistors**

## 2232

NPN Silicon Surface Mount Transistor with Monolithic Bias Resistor Network

#### **Features**

- Simplifies Circuit Design

- Reduces Board Space and Component Count

Marking: A8J

R1=4.7k, R2=4.7k

#### Description

This new series of digital transistors is designed to replace a single device and its external resistor bias network. The BRT (Bias Resistor Transistor) contains a single transistor with a monolithic bias network consisting of two resistors; a series base resistor and a base-emitter resistor. The BRT eliminates these individual components by integrating them into a single device. The use of a BRT can reduce both system cost and board space. The device is housed in the SOT-23 package, which is designed for low power surface mount applications.

#### Maximum Ratings (T<sub>a</sub>=25°C unless otherwise noted)

| ,                |                                                                       |            |            |  |

|------------------|-----------------------------------------------------------------------|------------|------------|--|

| Symbol           | Parameter                                                             | Value      | Unit       |  |

| V <sub>СВО</sub> | Collector base voltage                                                | 50         | V          |  |

| VCEO             | Collector emitter voltage                                             | 50         | V          |  |

| lc               | Collector current                                                     | 100        | mA         |  |

| P <sub>D</sub>   | Total Power Dissipation @ T <sub>A</sub> = 25°C  1) Derate above 25°C | 246<br>1.5 | mW<br>°C/W |  |

#### Note

### **Thermal Characteristics**

| The final characteristics         |                                             |              |      |  |  |  |  |

|-----------------------------------|---------------------------------------------|--------------|------|--|--|--|--|

| Symbol                            | Parameter                                   | Value        | Unit |  |  |  |  |

| Reja                              | Thermal Resistance - Junction-to-Ambient 1) | 508          | °C/W |  |  |  |  |

| T <sub>J</sub> , T <sub>stg</sub> | Operating and Storage Temperature Range     | - 55 to +150 | °C   |  |  |  |  |

| TL                                | Maximum Temperature for Soldering Purposes, | 260          | °C   |  |  |  |  |

|                                   | Time in Solder Bath                         | 10           | Sec  |  |  |  |  |

www.szlongjing.com A Dec. 2016

<sup>1.</sup> Device mounted on a FR-4 glass epoxy printed circuit board using the minimum recommended footprint.

Electrical Characteristics (T<sub>a</sub>=25°C unless otherwise specified)

| Symbol                         | Parameter                                         | Test Conditions                                    | Min | Тур | Max  | Unit |  |  |  |  |

|--------------------------------|---------------------------------------------------|----------------------------------------------------|-----|-----|------|------|--|--|--|--|

| Off Chara                      | Off Characteristics                               |                                                    |     |     |      |      |  |  |  |  |

| V <sub>(BR)CBO</sub>           | Collector-Base Breakdown Voltage                  | I <sub>C</sub> = 10 μA, I <sub>E</sub> = 0         | 50  |     |      | V    |  |  |  |  |

| V <sub>(BR)CEO</sub>           | Collector-Emitter Breakdown Voltage <sup>2)</sup> | I <sub>C</sub> = 2.0 mA, I <sub>B</sub> = 0        | 50  |     |      | >    |  |  |  |  |

| Ісво                           | Collector-base cut-off current                    | $V_{CB} = 50V, I_{E} = 0$                          |     |     | 0.1  | μΑ   |  |  |  |  |

| Iceo                           | Collector-emitter cut-off current                 | V <sub>CE</sub> = 30V, I <sub>B</sub> =0           |     |     | 0.5  | μΑ   |  |  |  |  |

| I <sub>EBO</sub>               | Emitter-base cut-off current                      | $V_{EB} = 6V, I_{C} = 0$                           |     |     | 1.5  | mA   |  |  |  |  |

| h <sub>FE</sub>                | DC current gain                                   | V <sub>CE</sub> = 10V, I <sub>C</sub> = 5mA        | 15  |     | 30   |      |  |  |  |  |

| V <sub>CE(sat)</sub>           | Collector-emitter saturation voltage              | I <sub>C</sub> = 10mA,I <sub>B</sub> = 1mA         |     |     | 0.25 | V    |  |  |  |  |

| On Characteristics             |                                                   |                                                    |     |     |      |      |  |  |  |  |

| VoL                            | Output Voltage (on)                               | $V_{CC} = 5.0V, V_B = 2.5V,$<br>$R_L = 1.0k\Omega$ |     |     | 0.2  | V    |  |  |  |  |

| Vон                            | Output Voltage (off)                              | $V_{CC} = 5.0V, V_B = 0.5V,$<br>$R_L = 1.0k\Omega$ | 3.3 | 4.7 | 6.1  | >    |  |  |  |  |

| R <sub>1</sub>                 | Input Resistor                                    |                                                    | 7   | 10  | 13   | kΩ   |  |  |  |  |

| R <sub>1</sub> /R <sub>2</sub> | Resistor Ratio                                    |                                                    | 0.8 | 1.0 | 1.2  |      |  |  |  |  |

<sup>2.</sup> Pulse Test: Pulse Width < 300  $\mu$ s, Duty Cycle < 2.0%.

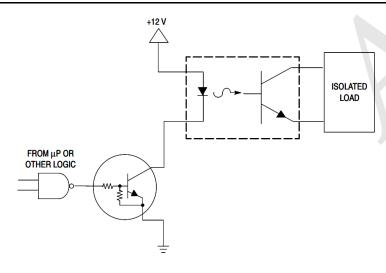

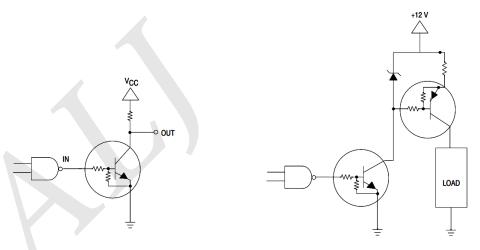

## **Typical Applications For NPN BRTs**

Figure 1. Level Shifter: Connects 12 or 24 Volt Circuits to Logic

Figure 2. Open Collector Inverter: Inverts the Input Signal

Figure 3. Inexpensive, Unregulated Current Source

www.szlongjing.com A Dec. 2016

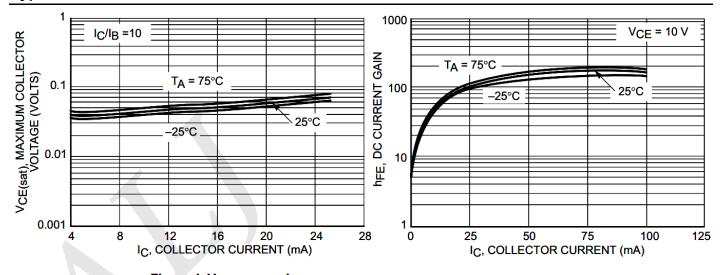

Figure 4. V<sub>CE(sat)</sub> vs. I<sub>C</sub>

Figure 5. DC Current Gain

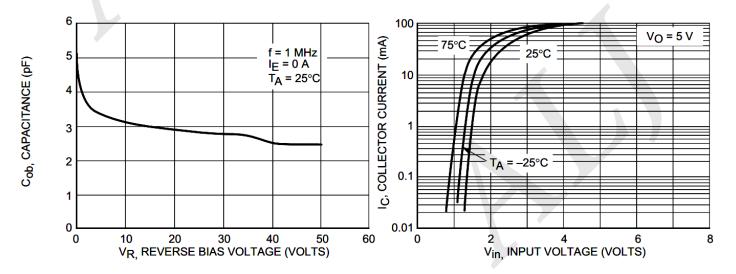

Figure 6. Output Capacitance

Figure 7. Output Current vs. Input Voltage

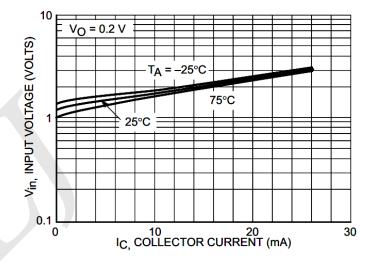

Figure 8. Output Voltage vs. Input Current

www.szlongjing.com A Dec. 2016